- 您现在的位置:买卖IC网 > Sheet目录342 > MCBSTM32EXL (Keil)BOARD EVALUATION FOR STM32F103ZE

�� �

�

�

�Flexible� static� memory� controller� (FSMC)�

�RM0008�

�SRAM/NOR-Flash� write� timing� registers� 1..4� (FSMC_BWTR1..4)�

�Address� offset:� 0xA000� 0000� +� 0x104� +� 8� *� (x� –� 1),� x� =� 1...4�

�Reset� value:� 0x0FFF� FFFF�

�This� register� contains� the� control� information� of� each� memory� bank,� used� for� SRAMs,� ROMs�

�and� NOR� Flash� memories.� When� the� EXTMOD� bit� is� set� in� the� FSMC_BCRx� register,� then�

�this� register� is� active� for� write� access.�

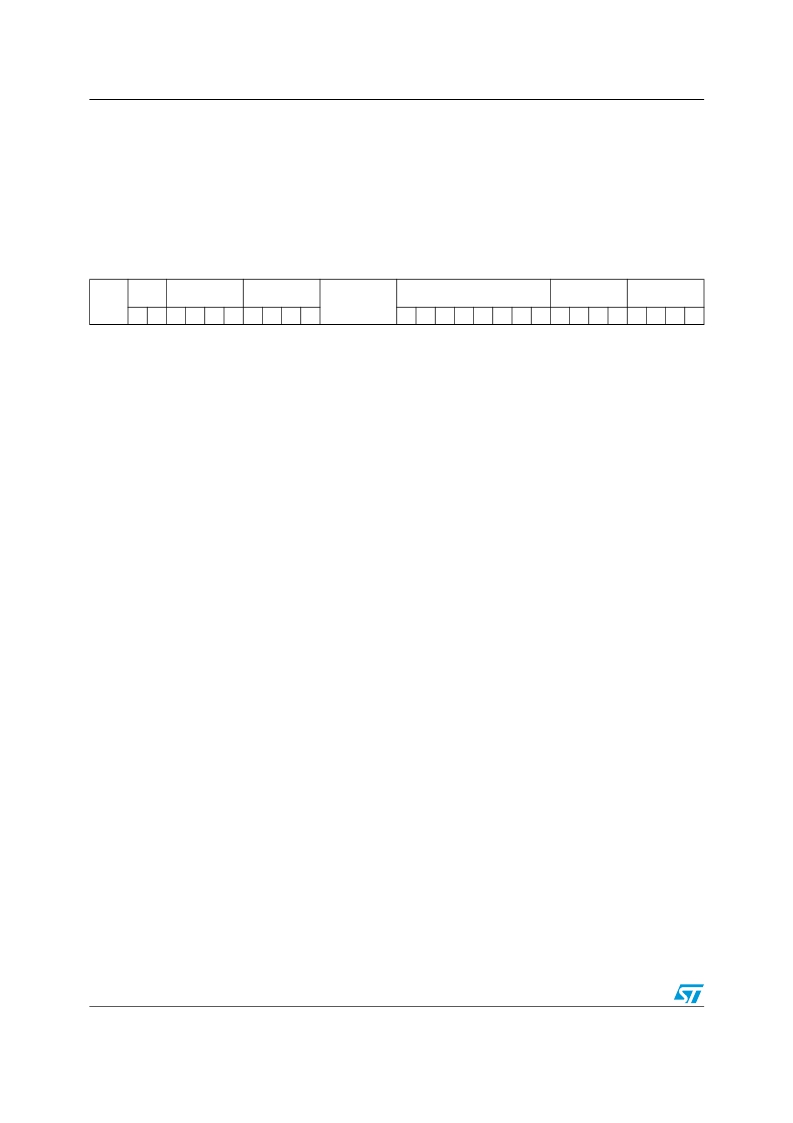

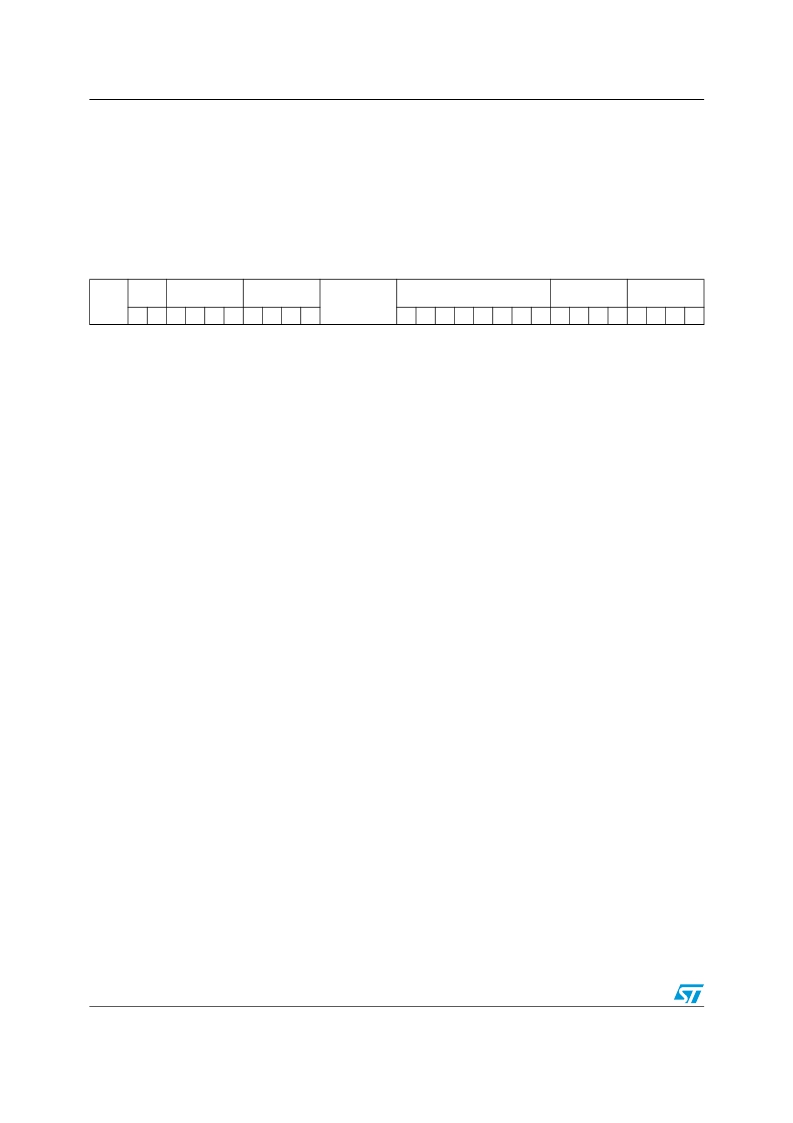

�31� 30� 29� 28� 27� 26� 25� 24� 23� 22� 21� 20� 19� 18� 17� 16� 15� 14� 13� 12� 11� 10�

�9�

�8�

�7�

�6�

�5�

�4�

�3�

�2�

�1�

�0�

�Res.�

�ACCM�

�OD�

�DATLAT�

�CLKDIV�

�Reserved�

�DATAST�

�ADDHLD�

�ADDSET�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�rw�

�Bits� 29:28� ACCMOD:� Access� mode.�

�Specifies� the� asynchronous� access� modes� as� shown� in� the� next� timing� diagrams.These� bits� are�

�taken� into� account� only� when� the� EXTMOD� bit� in� the� FSMC_BCRx� register� is� 1.�

�00:� access� mode� A�

�01:� access� mode� B�

�10:� access� mode� C�

�11:� access� mode� D�

�Bits� 27:24� DATLAT:� Data� latency� (for� synchronous� burst� NOR� Flash).�

�For� NOR� Flash� with� Synchronous� burst� mode� enabled,� defines� the� number� of� memory� clock� cycles�

�(+2)� to� issue� to� the� memory� before� getting� the� first� data:�

�0000:� (0x0)� Data� latency� of� 2� CLK� clock� cycles� for� first� burst� access�

�...�

�1111:� (0xF)� Data� latency� of� 17� CLK� clock� cycles� for� first� burst� access� (default� value� after� reset)�

�Note:� This� timing� parameter� is� not� expressed� in� HCLK� periods,� but� in� Flash� clock� (� CLK� )� periods�

�Note:� In� asynchronous� NOR� Flash,� SRAM� or� ROM� accesses,� this� value� is� don’t� care.�

�Note:� In� case� of� CRAM,� this� field� must� be� set� to� 0�

�Bits� 23:20� CLKDIV:� Clock� divide� ratio� (for� CLK� signal).�

�Defines� the� period� of� CLK� clock� output� signal,� expressed� in� number� of� HCLK� cycles:�

�0000:� Reserved�

�0001� CLK� period� =� 2� � HCLK� periods�

�0010� CLK� period� =� 3� � HCLK� periods�

�1111:� CLK� period� =� 16� � HCLK� periods� (default� value� after� reset)�

�In� asynchronous� NOR� Flash,� SRAM� or� ROM� accesses,� this� value� is� don’t� care.�

�Bits� 19:16�

�Reserved�

�Bits� 15:8� DATAST:� Data-phase� duration.�

�These� bits� are� written� by� software� to� define� the� duration� of� the� data� phase� (refer� to� Figure� 162� to�

��0000� 0000:� Reserved�

�0000� 0001:� DATAST� phase� duration� =� 2� � HCLK� clock� cycles�

�0000� 0010:� DATAST� phase� duration� =� 3� � HCLK� clock� cycles�

�...�

�1111� 1111:� DATAST� phase� duration� =� 16� � HCLK� clock� cycles� (default� value� after� reset)�

�440/995�

�Doc� ID� 13902� Rev� 9�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCBTMPM330

BOARD EVAL TOSHIBA TMPM330 SER

MCIMX25WPDKJ

KIT DEVELOPMENT WINCE IMX25

MCIMX53-START-R

KIT DEVELOPMENT I.MX53

MCM69C432TQ20

IC CAM 1MB 50MHZ 100LQFP

MCP1401T-E/OT

IC MOSFET DRVR INV 500MA SOT23-5

MCP1403T-E/MF

IC MOSFET DRIVER 4.5A DUAL 8DFN

MCP1406-E/SN

IC MOSFET DVR 6A 8SOIC

MCP14628T-E/MF

IC MOSFET DVR 2A SYNC BUCK 8-DFN

相关代理商/技术参数

MCBSTM32EXLU

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINK2 FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32EXLU-ED

制造商:ARM Ltd 功能描述:KEIL STM STM32EXL EVAL BOARD

MCBSTM32EXLUME

功能描述:开发板和工具包 - ARM EVAL BOARD + ULINKME FOR STM32F103ZG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200U

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG + ULINK2

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F207IG ULINK-ME

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V

MCBSTM32F200UME-ED

制造商:ARM Ltd 功能描述:KEIL STM32F207IG EVAL BOARD

MCBSTM32F400

功能描述:开发板和工具包 - ARM EVAL BOARD FOR STM STM32F407IG

RoHS:否 制造商:Arduino 产品:Development Boards 工具用于评估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口类型:DAC, ICSP, JTAG, UART, USB 工作电源电压:3.3 V